# 11 Chapter 11 Designing with MSI-LSI

# 11.1 Introduction

Once a set of design constraints have been established, there are several options available to the designer to be used in implementation. Circuit built with SSI-level logic may be faster, may be minimal in parts count, may be irreducible, and, therefore, may be more testable than those built using MSI or LSI devices.<sup>1</sup> SSI-level designs take a relatively longer time to develop, debug, and document. It is acknowledged to be the most difficult. The criteria that determine the desirability of doing an implementation with SSI-level logic are:

1. The required speed is faster than would be available with any other implementation;

and

2. The anticipated production volume justifies the expense of doing an SSI-level design.

Where total testability is not a major concern, as is true for most commercial-level applications, MSI design with multiplexers and functions blocks (think IP) is attractive (reduces TTM – time to market). While multiplexers are nonminimal implementations of their output functions, which constrain their testability, they are easier to deal with and allow reduction in board space.<sup>2</sup> Speed and power requirements are the determining factors in choosing to use multiplexers and other MSI function blocks.

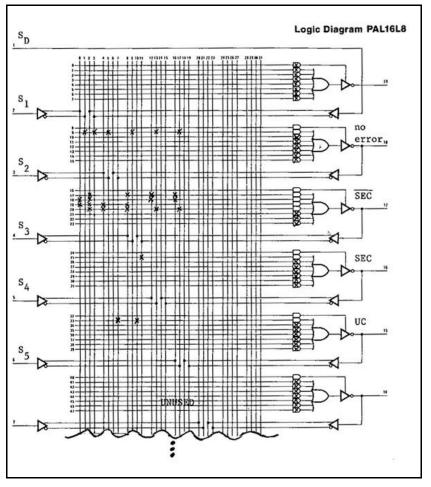

Programmable multiplexers (PMUXs), gate arrays (PGA, CGA), logic arrays (PLA, FPLA) and array logic devices (PAL) are available now in a number of configurations and sizes. Most of these are intended to assist in reducing the parts count for implementation of combinational functions. Some of the PALs have registered outputs and feedback paths and are for use in sequential logic implementation. All of there devices are contributing toward modular hardware designs.

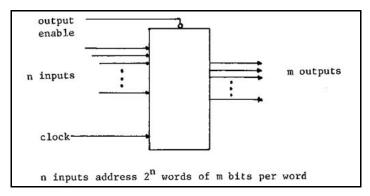

Sequential control functions may be implemented with microprograms using PROM/ROMs with the more complex controls using a microprogram sequencer.<sup>3</sup> Higher-speed control functions are being implemented using bipolar bitslice devices (such as the Am2910), while less speed-restricted applications use one or more of the microprocessor/microcomputers (such as the Intel 8085). All of these devices are considered to be LSI and all of them require a software investment. The bit-slice devices require microprogramming, which may be accomplished with a pseudo-assembly –level language and a development system. [Meta-assembler.] The fixed-instruction-set microcomputers are programmable in assembly or higher-level languages, with some of the new devices to be programmed in *PASCAL* or a similar algorithmic language. [Today it would be C<sup>++</sup> or Pearl.]

As the implementation shifts from SSI to LSI, software design techniques, specifically modularity and structured programming, begin to become mandatory. Testing is no longer a hardware checkout operation, but requires software diagnostic packages. One advantage of LSI is the feasibility of putting the system diagnostic routines on-board the PROMs, to simplify design debug and field testing.

<sup>&</sup>lt;sup>1</sup> Applies to the density levels of RTL in today's design kit.

<sup>&</sup>lt;sup>2</sup> This discussion was originally based on discrete design. Mid-1970s. MSI and LSI were in vogue, LSI was being thought of, and ASICs hadn't arrived with a vengeance as yet.

Software development costs in computer systems have far exceeded those of hardware development. This trend is being repeated in LSI designs with the microprogramming development costs overriding the hardware costs.

# 11.2 SSI Design

To develop a minimal or optimal two- or three-level NAND logic circuit, with the third level for inversion of the logical variables, the equation of function y must be solved for its minimal  $\Sigma\Pi$ -form. This is accomplished using the APL function:

MINIMA (Z 1)

which produces the desired expression.

To develop a minimal or optimal two- or three-level NOR logic circuit, the equation of the function y must be solved for its  $\Pi\Sigma$  form. This is accomplished by using the APL function:

MINIMA ( $\underline{Z}$  1)

which produces the desired expression.

Conversion techniques exist for NOR-to-NAND and for NAND-to-NOR without restarting from the original expressions of the function y (refer to any text for a beginning course in logic design); however, the resulting network is not guaranteed to be minimal. Where an expression is factorable to produce terms of the form  $(a \underline{b} + \underline{a} b)$ , EXOR gates may be used to reduce gate count and to simplify implementation.

Fan-in requirements can be achieved by factoring the minimal  $\Pi\Sigma$  or  $\Sigma\Pi$  forms. The fan-in requirements present in early SSI designs are more relaxed today with the allowances of eight (8) or more inputs allowed per gate. [The dragging of the load on the gate performance is, however, still problematic.] Fan-out requirements are generally alleviated by the use of buffer-drivers, and duplicate parallel paths. Present designs<sup>4</sup> use a conservative limit of seven (7) loads per output for devices rated at 10 loads.

# 11.3 Gate versus Connection Minimization

Muruga and Lai (*Muruga and Lei, "Minimization of Logic Networks under a Gneralized Cost Function", IEEE Trans., Sept. 1976, pp. 7893-907)* reported on the calculations of the minimal networks for NOR gates for all functions of 3 or fewer variables, and for some of the functions of 4 variables. For the 77 P-equivalence non-trivial class representative functions of 3 or fewer variables, there are only two functions for which the minimal networks under GCM (gate reduction emplasis) and CGM (connection reduction emphasis) differ.

They are:

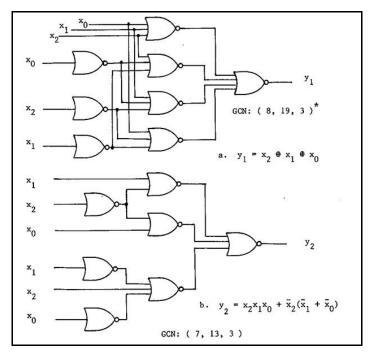

$$\textbf{Y}_1 = \textbf{X}_2 \oplus \textbf{X}_1 \oplus \textbf{X}_0$$

and

$$\mathbf{Y}_2 = \mathbf{X}_2 \mathbf{X}_1 \mathbf{X}_0 + \underline{\mathbf{X}}_2 \left( \underline{\mathbf{X}}_1 + \underline{\mathbf{X}}_0 \right)$$

(Underlining equals negation)

For these two functions, the minimal  $\Pi\Sigma$  form was investigated and found to give:

- the same number of gates as does the GCM reduction

- more connections than does the CGM version

- and fewer stages (gate levels and, therefore, gate delays).

The GCM reduction reduces the gate count by one over the minimal  $\Pi\Sigma$  form, but increases the connections by one. In one case, there is an added stage delay.

The minimal  $\Pi\Sigma$  forms of the two functions are shown in *Figure 11-1* a and b. A table comparing the various implementations in terms of number of gates, number of connections, and number of levels, is shown in *Table 11-1*.

<sup>&</sup>lt;sup>4</sup> 1970s – late 1970s

= (# Gates, # Connections, # Gate Levels)

Table 11-1 Minimal  $\Pi\Sigma$  forms of  $y_1$  and  $y_2$  Compared

| Function | Minimal    | GCM        | CGM        |

|----------|------------|------------|------------|

| y1       | (8, 19, 3) | (7, 20, 4) | (8, 16, 6) |

|          |            |            | (8, 16, 5) |

|          |            |            | (8, 16, 6) |

| y2       | (7, 13, 3) | (6, 14, 3) | (7, 12, 4) |

|          |            |            | (7, 12, 5) |

Among 312 representative functions of P-equivalence classes of 4 variables requiring at most 5 NOR gates under GCM, 26 functions were found to have different minimal networks under CGM design constraints.

Of the 26 functions:

- 1) For 4 of the functions, they had GCM and CGM minimal networks where the number of gates levels or stages were equal. In 22 cases, the number of levels was at least one higher for CGM design constraints.

- 2) For 7 of the functions, that were implemented in CGM, CGM had a gate count higher then the GCM version (higher by 1).

- 3) For 8 of the functions implemented in CGM, CGM had 2 fewer connections then the GCM versions of those functions. The rest had a connection count that was lower by 1.

- 4) For some of the functions, a gate count for the GCM version lower than the minimal  $\Pi\Sigma$  form version was obtained by the introduction of redundancy, which in turn reduced testability.

- 5) For some of the functions, a gate count reduction was accomplished through the use of a factored, equivalent form which added one gate level.

Their conclusion was to use the gate criteria in minimization and design. (They were concerned specifically with chip area, i.e., die size, in their paper.). Our conclusion is to use the minimal  $\Pi\Sigma$  and  $\Sigma\Pi$  forms, factoring where possible for reduction but maintaining irredundancy (i.e., no redundancy allowed).

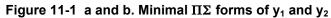

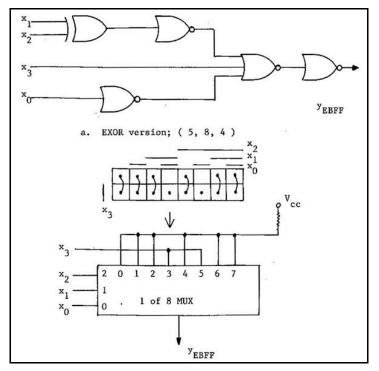

The length of time available to design the network is an overriding constraint in all cases. For the minimal  $\Pi\Sigma$  and  $\Sigma\Pi$  forms, the APL function MINIMA is available as a design tool. *Figure 11-2* examines three implementations of the function Muruga and Lai indexed as EBFF. (Their index uses HEX notation to fill in the rows of a 4-variable Marquand map.) It represents the minimal  $\Pi\Sigma$  form, a GCM (minimal gate) version, and a CGM (minimal connection) version of the function.

Figure 11-2 Comparison of SSI Implementations

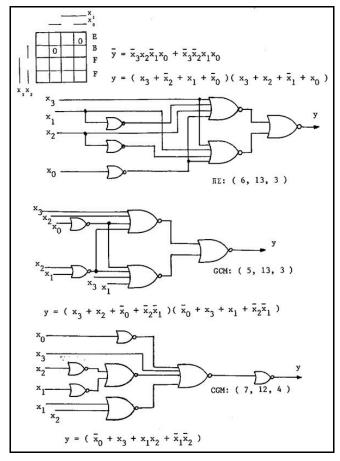

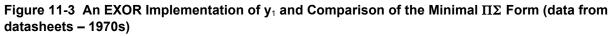

For the two functions of three variables  $Y_1$  and  $Y_2$  described earlier, the SSI implementation of  $Y_1$  is improved by using EXOR gates. (*Figure 11-3.*) A comparison between the implementation of the minimal  $\Pi\Sigma$  form of y in NOR gates and the EXOR implementation is shown in *Table 11-2*.

| ltem            | Minimal $\Pi\Sigma$ NOR | EXOR  |

|-----------------|-------------------------|-------|

| Cost            | 0.80                    | 0.40  |

| Levels          | 3                       | 2     |

| Packages`4      | 1                       |       |

| Time<br>(Speed) | 32ns                    | 28ns  |

| Power           | 56mW                    | 150mW |

## 11.4 MSI Design

The decision to use SSI or MSI is dependent upon the complexity of the function being impolemented and upon esign constraints such as timing, board space, and power consumption.

Multiplexer chips<sup>5</sup> for 3, 4 and 5 variables are easy to use and input requirements can be read directly from the Marquand Map of the function. (Karnough Maps require permutation of certain columns to achieve a column-to-input order and are, therefore, not recommended here.) Muxs are available in some cases with true and complimented outputs and have 1, 2, or 3 chip-select or enable pins ( $S_0$ ,  $S_1$ ,  $S_2$ ), providing design flexibility.

Multiplexers are formed internally from two-level logic, which makes them competitive in speed with SSI gate implementations. In some cases, they may even be faster than SSI doe to the reduction of interpackage<sup>6</sup> time delays.

The use of multiplexers reduces package count at the cost of increased power consumption per package. [Reduces macro count at the cost of increased power for the more complex macro.]

<sup>&</sup>lt;sup>5</sup> for today read "macros"

<sup>&</sup>lt;sup>6</sup> for today, read "intermacro" or "interconnect" delay

The other factors that must be considered are:

- 1) The number of connections

- 2) The loading on the variables

- 3) the loading on power and ground

The use of multiplexers may or may not render the design "flexible", i.e., able to be altered with changes in requirements and specifications. Any function implemented in multiplexers is not necessarily minimal. Coverage will be column-minimal and the cost of possible increased loading. *Figure 11-4* presents the one-of-four multiplexer in detail and an example derivation of input functions using a Marguand Map.

Figure 11-4 One-of-Four Multiplexer

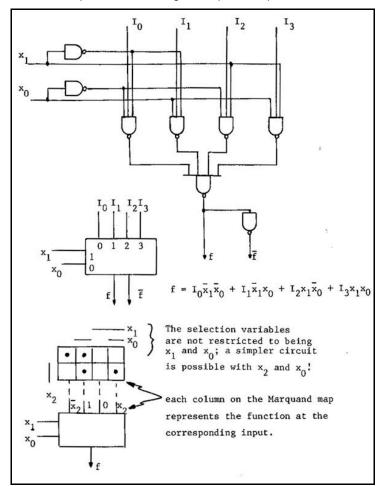

*Figure 11-5* presents the multiplexer implementations of Y1 and Y2 and a table summarizing the differences between the multiplexer, NOR Gate, and EXOR implementations is shown in *Table 11-3*.

Figure 11-5 Implementation of y1 and y2 with Multiplexers

| Item           | Value  | Comment                                    |

|----------------|--------|--------------------------------------------|

| Time Delay:    | 21ns   | faster than a NOR gate (in the late 1970s) |

| Power:         | 200mW  | More Power, More Heat                      |

| Package count: | 1      | Same as for EXOR version                   |

| Cost:          | \$1.50 | (approx) – More Expensive                  |

Table 11-3 Comparing the Implementations:

Differences between the multiplexer, NOR Gate, and EXOR implementations – See Table 11-2.

Multiplexer sizes are of 1-of-2, 1-of-4, 1-of-8 and 1-of-16 (an oversized chip in those days). When a function larger than five variables is to be implemented, multiplexers may be cascaded.

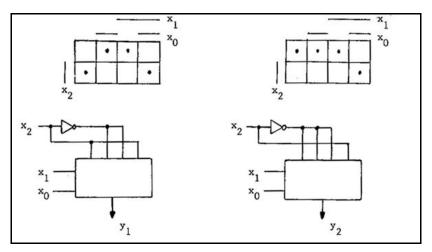

The 4-variable function EBFF is shown in *Figure 11-6a*, implemented using an EXOR gate to improve the connection count (8 instead of 12 for the same number of gates) at the expense of an added level and its delay.

*Figure 11-6b* shows the clean simplicity of a multiplexer implementation of the same function and the associated Marquand Map.

b. Multiplexer Version: (1, 11, 1)

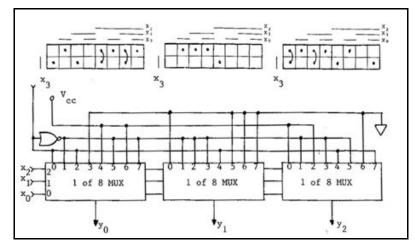

Multiple-output problems are designed faster using multiplexers. The problem discussed in Chapter 8 and shown in Figure 8 (reference) is shown implemented with multiplexers in *Figure 11-7*. Included is a table (*Table 11-4*) comparing:

- 1) The individual output function SSI version

- 2) A reduced multiple-output SSI version

- 3) and a multiplexer version

The multiplexer version in this case

- 1) runs slightly faster

- 2) has fewer connections

- 3) uses less board space

- 4) can be designed relatively faste

- 5) and is easily debugged

- 6) all at a cost of 2-4 times the power consumption.

The choice is dependent upon the design constraint of specified allowable power consumption and heat dissipation capability.

Figure 11-7 Multiplexer Implementation of the Multiple Output Problem

| Version       | Gates        | Packages | Connections | Spares         | Levels | Power<br>(mW) | Speed<br>(ns) |

|---------------|--------------|----------|-------------|----------------|--------|---------------|---------------|

| SSI           | 17           | 6        | 43          | 0              | 3      | 170           | 30            |

| Mult.<br>Out. | 15           | 6        | 38          | 3<br>gates     | 3      | 150           | 30            |

| MUX           | 3 MUX<br>+ 1 | 4        | 34          | 5<br>inverters | 2      | 685           | 18            |

|               |              |          |             |                |        | 445           | 26            |

Table 11-4

Multiple Output Problem Implementation Comparison

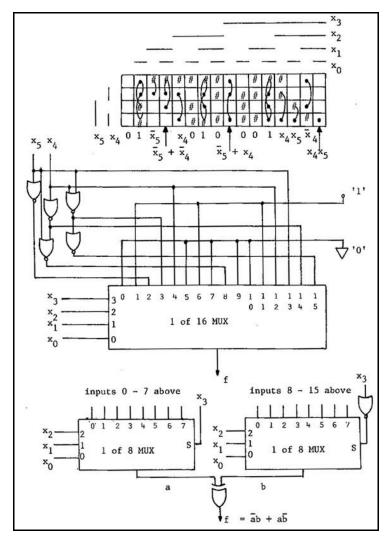

As more variables are introduced, choices in which multiplexers to use are added. The six-variable example discussed in Chapter 8 is implemented using a 1-of-16 MUS and again using 1-of-8 MUIXs in *Figure 11-8*

The map of the function, its equation, and a table comparing the three implementations --- SSI and the two MUX versions --- are presented in *Figure 11-9* and *Table 11-5*.

Figure 11-8 Svoboda's Six-Variable Example done with Multiplexers

Figure 11-9 Six-Variable Marquand Map for the Example

The equation is:

$$y = \bar{x}_5 x_3 \bar{x}_1 x_0 + \bar{x}_4 \bar{x}_3 x_1 \bar{x}_0 + \bar{x}_4 x_2 x_1 \bar{x}_0 + \bar{x}_5 \bar{x}_3 \bar{x}_2 x_0 + \bar{x}_5 \bar{x}_2 x_1$$

$$+ \bar{x}_3 x_2 \bar{x}_0 + x_5 x_3 \bar{x}_2 x_0 + x_5 x_4 x_3$$

Table 11-5 Comparison of Implementations of the Six-Variable Example

| Version                          | Stages | Connections | Packages | Time/speed | Power | Approx. Cost |

|----------------------------------|--------|-------------|----------|------------|-------|--------------|

| SSI (NAND)                       | 3      | 43          | 6        | 30ns       | 220mW | 1.20         |

| MSI, 1-of-8<br>MUX, NOR,<br>EXOR | 4      | 37          | 4        | 51ns       | 500mW | 2.60         |

| MSI, 1-of-16<br>MUX, NOR,<br>INV | 4      | 28          | 3        | 41ns       | 316mW | 1.80         |

(Data from datasheets (late 1970s), Numbers are Typical Case)

# 11.5 LSI Design Techniques

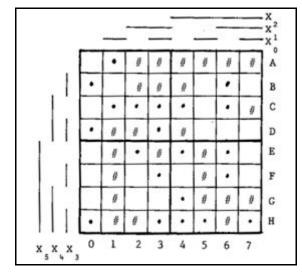

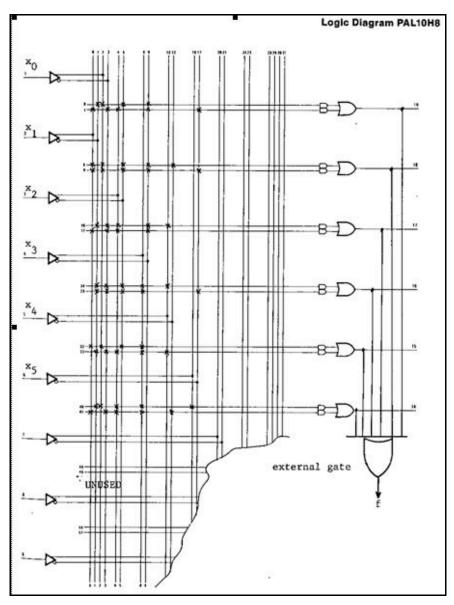

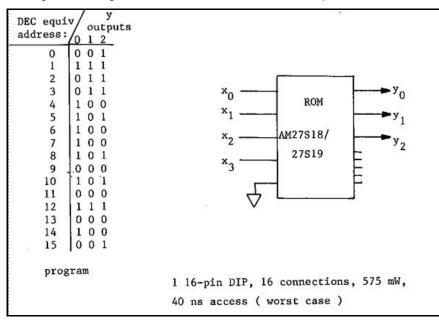

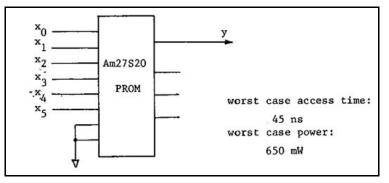

There are in existence a number of microprogrammable devices which may be used to reduce parts count and, therefore, required board space. A few examples of the most common of these are called out in *Table 11-6* Programmable devices, with the exception of ROMs, are effective in design situations where the number of input variables is large and the number of active logic states is small --- that is, in cases where the logical map of the function is sparsely populated.

| Device                    | Example Product (late 1970s)                                                        |

|---------------------------|-------------------------------------------------------------------------------------|

| Programmable Multiplexers | Raytheon 29693 PMUX (10 inputs, 1 term/MUX input, 4<br>1-of-8 MUXs)                 |

| FPLA                      | Signetics N82S101/10 (16 inputs, 48 terms, 8 outputs, 50ns)                         |

| PLA                       | National DM 75 7516 (19 inputs, 70 terms, 8 outputs, 150ns)                         |

| PAL                       | Monolithic Memories PAL10H8 (10 inputs, 8 outputs, 4 registeresd outputs, 64 terms) |

| Registered PAL            | Monolithic Memories PAL16X4 (8 inputs, 8 outputs, 4 registered outputs, 64 terms)   |

| ROM: EROM                 | Signetics SN 74S271/371 (256x8 with 45ns Access Time)                               |

| ROM: PROM                 | Signetics SN 74S271/371 (256x8 with 45ns Access Time)                               |

| ROM: Registered ROM       | AMD Am27S26/27 (512x8 with 20ns Cp-to-Output time – prelim)                         |

Table 11-6 Examples of Microprogrammable Devices (late 1970s)

## 11.5.1 Programmable Multiplexers

One of the programmable is the Raytheon 29693 PMUX listed in Table ----. This device has 10 inputs, all inverted, and 4 inverted outputs. Logically it is equivalent to four 1-of-8 multiplexers with OR gates at each of the 10 inputs. The multiple-output problem presented earlier is of the type suitable for a PMUX implementation because:

- 1) The MUXs have common select lines

- 2) The number of input variables is less than 10

Figure 11-7 is very nearly a program for the 29693 PMUX. The only change required is to use X3 + X3 as the input where Vcc is shown. Documentation of this device is one to four Marquand Maps (one for each output used) drawn with select variables as column indices and inpout variables as row indices. Note that an external inverter for X3 would be required. Note also that this example under-utilizes the PMUX ability and is for demonstration only (this would never be built).

## 11.5.2 Programmable Logic Arrays

A programmable logic array (PLA) is an LSI implementation of the classic digital net, a sum-of-products form for positive logic. It is general-purpose and user-definable within limits. Both the variable composition of the individual product terms and the assignments of the terms to different outputs are specified by the designer.

PLAs are characterized by the following attributes:

- 1) The number of inputs

- 2) Buffered or unbuffered inputs

- 3) The number of minterms or product terms

- 4) The number of outputs

- 5) The characteristics of the outputs: (late 1970s)

- a. TTL

- b. Open-Collector (OC)

- c. Tri-state

- 6) Programmable output inversion

- 7) Access time

There are two basic types of PLAs, determined by how they are programmed. A factory- or mask-programmed PLA is typically larger than 96 minterms. Factory programming uses the metal-mask technology.<sup>7</sup>

A field-programmable PLA (FPLA) typically has 48 minterms and may use one of three programming technologies:

- 1) Nichrome fuse

- 2) Polysilicon fuse

- 3) Avalanche induced migration

Given a PLA with the following characteristics:

- 1) 16 inputs, either true or inverted, to any AND gate

- 2) 8 outputs, either true ior inverted

- 3) 48 product terms to any OR gate

- 4) Typical access time of 50ns

- 5) Power dissipation of 620mW (Typ.)

- 6) 28-pin DIP (dual-in-line package) (approximate space of 3 16-pin DIPs)

<sup>&</sup>lt;sup>7</sup> sizing, technology will have varied by now of course, but the design principles remain.

The six-variable functions shown in *Figure 11-10a* are to be implemented. These functions are not necessarily minimal. These are, using the available parts above:

- 1) 6 inputs required

- 2) 14 product terms, of which 3 are seen to be identical

- 3) and 4 outputs.

If the equations given had not been in a sum-of-products form, expansion would have had to be performed to obtain this format as each output is a sum-of-products function. Internally the PLA is an AND-OR net with an inverter programmable at the output if desired.

For the functions shown in *Figure 11-10*a, a single PLA may be programmed as shown in *Figure 11-10*b. No minimization needs to be performed.

| $y_0 = x_0 x_1 x_2 +$                                                                     | $x_1x_3 + x_1x_2x_3x_4x_5 + x_1x_2x_3x_4x_5 + x_1x_2x_3x_4x_5 + x_1x_2x_3x_4x_5 + x_1x_2x_3x_4x_5 + x_1x_3x_4x_5 + x_1x_3x_5 + x_1x_5 + x_1x$ | 4 <sup>x</sup> 5                                      |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| $y_1 = x_2 \overline{x}_1 x_2 x_3$                                                        | $+\bar{x}_1\bar{x}_3 + \bar{x}_1x_4x_5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | must be in                                            |

|                                                                                           | 19 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ΣΠ form                                               |

| $y_2 = x_2 x_3 x_5 +$                                                                     | $\bar{x}_0 x_1 \bar{x}_2 x_3 \bar{x}_4 x_5 + \bar{x}_1 x_2 \bar{x}_5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |

| $y_3 = x_0 x_2 x_5 +$                                                                     | $\bar{x}_1 x_4 x_5 + \bar{x}_1 \bar{x}_3 + x_0 x_2 \bar{x}_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                     |

| a. The equat                                                                              | ions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                       |

| 4 functions                                                                               | PLA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | chosen has 4 outputs,                                 |

| 6 input vari                                                                              | ables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6 inputs,                                             |

| 14 terms                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 product terms                                      |

|                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                       |

| * * * * * * *                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | S - 15                                                |

| x <sub>0</sub> x <sub>1</sub> x <sub>2</sub> x <sub>3</sub> x <sub>4</sub> x <sub>5</sub> | <sup>y</sup> 0 <sup>y</sup> 1 <sup>y</sup> 2 <sup>y</sup> 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                     |

| 1 0 1 x x x                                                                               | 1 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| x 0 x 0 x x                                                                               | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

| x 1 1 0 1 0                                                                               | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       |

| x x x x 1 1                                                                               | 1 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 101xx1                                                                                    | 0 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| x 0 x 0 x x                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | one term, all that is                                 |

| x 0 x x 1 1                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | red to make the functions<br>he PLA ( in this case ). |

| x x 1 0 x 1                                                                               | 0 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 010101                                                                                    | 0 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| x 0 1 x x 0                                                                               | 0 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 1 x 1 x x 1                                                                               | 0 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| x 0 x x 1 1                                                                               | 0 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

| 1 x 1 x x 0                                                                               | 0 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                       |

|                                                                                           | b. T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | he PLA program.                                       |

#### Figure 11-10 Designing with a Small PLA

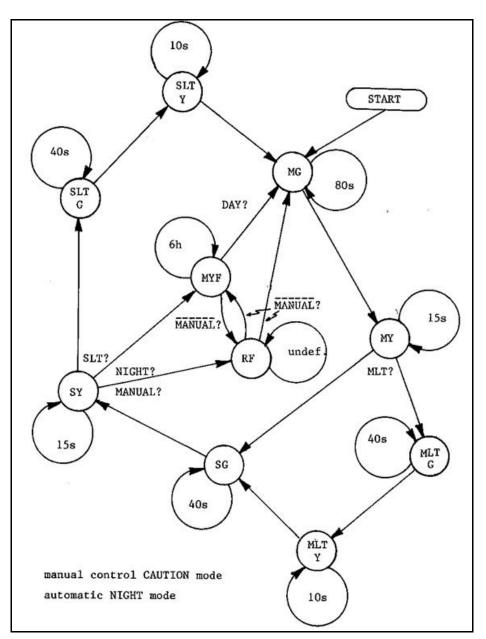

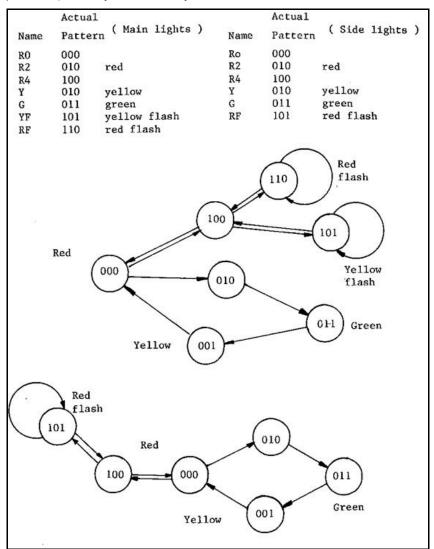

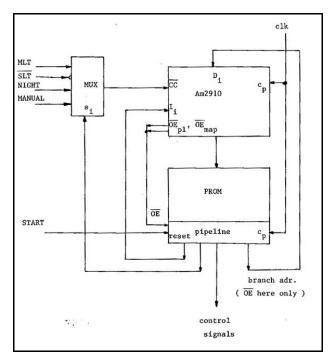

Svoboda's six-variable problem could easily be implemented with one PLA-type device. There are 20 product terms required, less than half the number available in the smallest of these devices. The product terms can be trivially taken from the Marquand Map of the function without minimization. The trade-offs are increased power consumption for less board space, a simpler design effort (design time), and reduced testability (as introduced by redundancy).